# Visualization of Verilog Digital Systems Models

K. Jelemenská, M. Nosáľ, P. Čičák

Institute of Computer Systems and Networks, Faculty of Informatics and Information Technologies

Slovak University of Technology Bratislava

Ilkovičova 3

842 16 Bratislava, Slovakia

jelemenska@fiit.stuba.sk; nosal.michal@gmail.com; cicak@fiit.stuba.sk

Abstract— Nowadays the digital systems design is almost exclusively realized using hardware description languages (HDL). Verilog belongs to the HDLs that are the most widespread especially in the United States. However, the textual HDL representation of structural model is less understandable compared the schematic one. Therefore a transformation of the structural HDL description into its graphical schematic representation is a useful function for hardware designers. In this paper the HDL Visualizator is described that was designed and implemented to support this function for Verilog structural models. The paper addresses several problems of visualization process and their possible solutions. The design and implementation of visualization tool that is able to display the schematic view as well as the simulation results of structural Verilog model is also presented.

# I. INTRODUCTION

In the process of complex digital systems design hardware description languages (HDLs) have an irrecoverable role. They provide designers the possibility to describe the hardware behavior and structure on the various abstraction levels. However, the structural description in HDL form is often unreadable for the persons not familiar with this kind of design. In these situations the tools for graphical visualization of HDL structural description are very useful.

There are several applications, design tools or development environments that are capable of graphical visualization of a design structure. This possibility is usually only one of many other functions available in the expensive and often too complex solutions for certain group of users, e.g. students or beginners in HDL design. There are very few, if any at all, easy-to-use and affordable applications offering HDL models visualization especially when they are written in Verilog. Our aim was to overcome this gap.

The problem of visualization of digital system Verilog structural description is the main subject of this paper. The paper covers application design, its implementation and testing results.

# II. RELATED WORK

The digital systems design methods have evolved dramatically over the last 30 years. The traditional design methods, based on mathematical equations or schematic approach to the hardware design, became impractical or even useless in the process of complex digital systems design.

Modern design methods based on HDLs and design automation tools brought the effectiveness into the design

process and sped it up substantially. Another tremendous advantage was the replacement of prototyping by simulation. The designers can model hardware structure and behavior on various abstraction levels using HDLs and simulate the model to verify its properties. Nowadays, a lot of professional automatic design tools provide several ways to describe digital system behavior and structure together with its optimization. They support various types of graphical and textual editors e.g. to enter the state diagrams, truth tables, logic diagrams or simply to describe the circuit in HDL. The most commonly used HDL languages are VHDL, Verilog and SystemC.

There are many implementations tools with wide spectrum of functions to make the design process easier, more effective and faster. However, most of the software tools capable of structure visualization described in Verilog are the commercial ones. To the most widespread belong Visual Elite, Active-HDL and HDL Author [1-3].

*HDL Author* is the product of Mentor Graphics company [1] that replaced the previously supported HDL Detective. The main goal of this tool is the improvement of team work and data exchange between team members therefore it was designed for data management in all phases of design process. The HDL code visualization function is just one of its many functions and enables also Verilog code conversion into a Block Diagram, IBD, State Diagram or Flow Chart. The objects layout, color, style, and font can be modified i.e. the non-logical edits can be applied that will not influence the original code in any way. However, HDL Author is a robust application, which is very complex and quite expensive.

Visual Elite was originally developed by Summit Design company and later bought by Mentor Graphics [2]. This is another complex and universal application to design and build products. It offers a variety of HDLs and other design entry methods including block diagrams, state diagrams and connectivity tables. It also provides automatic mapping of source code into graphical representation. However, the quality of code visualization is not as high as in HDL Author. On the other hand the user interface is very comfortable and easier to manage by new users, than relatively complicated HDL Author's user interface.

Another complex design system supporting HDL code visualization is Aldec's Active-HDL [3]. It is a suite of many tools covering all phases of FPGA design and verification. In the context of this paper the tool called Code2Graphics is an interesting one. This tool enables the HDL code conversion into a graphic representation that can be further edited. Unlike in HDL Author or Visual Elite, the altered graphic representation can be converted back to the text form of

arbitrary supported HDL using Graphics2Code tool. Moreover, Active-HDL also supports the visualization of simulation. During the simulation an actual state of every module in the block diagram is visualized and the values of all variables are visible in the waveforms. In many other ways Active-HDL is comparable to Visual Elite.

All the mentioned tools and systems are the commercial ones. They all provide many functions, including visualization, and support several HDLs. The main issue is their excessive complexity and the price which is often not affordable for beginners and students.

Since the problem of lost clarity in textual description of structure is especially relevant to students and beginners, we decided to dedicate our effort to the development of simple and easy to use tools for HDL structural description visualization. Several solutions have been developed at the Faculty of Informatics and Information Technologies, Slovak University of Technology (FIIT STU) in Bratislava, most of them in the frame of diploma theses [4, 6, 7, 8].

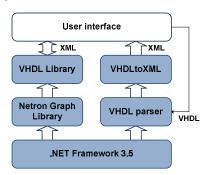

VHDLVizualizer [4] is the tool dedicated to the VHDL structural description visualization. The architecture of this solution consists of six components (see Fig. 1). The VHDL parser was built by ANTLR (ANother Tool for Language Recognition) that provides a framework for arbitrary language parser generation based on its grammar definition [5]. The graphic user interface is based on Netron Graph Library and an XML (Extensible Markup Language) format is used to represent the visualized VHDL description internally.

The tool is able to check the VHDL source code syntax and to visualize the VHDL structural description preserving its hierarchy. It also supports basic non-logical editing of the resulting visualization like modules layout modification, modules connections formatting, notes insertion etc. The created diagrams can be exported into jpeg files or saved in XML file. The main limitation of this solution was the quality of the displayed layout of modules and especially the interconnections which was far from ideal. This issue was discussed and partially solved in [6].

Another solution with the functionality similar to VHDLVizualizer was called *VHDL Visualizator* [7]. The system architecture is basically the same but this tool was implemented on Delphi and Java platforms. An internal representation of visualized structure is also based on XML format. Although the quality of visualization is a bit higher in this case, the tool supports smaller subset of VHDL.

An interesting solution represents [8] that was focused on the SystemC models visualization, based on the modifications of SystemC library itself. However, the SystemC nature is substantially different from other HDLs, therefore the approach

Fig. 1. The VHDLVisualizer architecture

adopted in this solution can not be used for Verilog models visualization.

The visualization tools already developed at FIIT STU Bratislava were devoted to VHDL and SystemC HDL languages. The third commonly used HDL – Verilog was not yet supported. This work is supposed to overcome this gap.

## III. VISUALISATION OF STRUCTURAL HDL DESCRIPTION

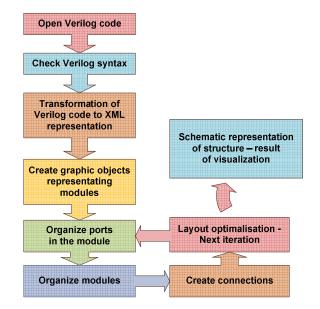

In the context of HDL structural description visualization, the important language constructs are module definitions, port definitions, module instances and their mutual connections. In schematic representation each module is represented by a graphical entity with ports that are connected with ports of other modules. The visualization process is illustrated in Fig. 2. There are three main problems that have to be solved in the visualization process: syntactic analysis of Verilog code, internal data representation, and graphical layout of the visualized data.

The first step in the visualization process is a conversion of Verilog source code into its internal representation. During this step two issues have to be addressed: Verilog code *syntactic analysis* and *internal representation* selection. An appropriate internal representation should be able to keep the information about the modules and connections position, size and general layout. From this step the third issue results: the optimization of modules and connections *graphical layout*.

#### A. Syntactic Analysis of Verilog Code

Syntactic analysis is relatively complicated but an unavoidable step in the visualization process. However, there is a possibility to use an existing parser for this purpose. Several freeware tools are available supporting among other functions Verilog syntax checking [9]. *Icarus Verilog* is a tool for Verilog simulation and synthesis. *Source Navigator for Verilog* is an open source development environment for Verilog which has a built in parser. *CvSDL* represents C++ libraries for Verilog simulation. *GPL Cver* denotes another Verilog simulator with full support of IEEE 1364-1995 Verilog standard and partial support of Verilog 2001. *Verilog2C*++ is a tool performing Verilog code transformation into its C++

Fig. 2. The visualisation process of HDL structural description

equivalent. Finally, *Verilator* stands for Verilog simulator suitable for large projects, where simulation performance is the primary concern.

From the available freeware tools the *Icarus Verilog* was identified as the most suitable for our purpose, since in addition to the syntactic analysis it enables also to use the simulation results in our visualization tool.

The next step in the process of visualization is the transformation of Verilog description into its internal representation, what should be done by parser. Since we were not able to find a suitable open source parser for Verilog language, we were considering the available parser generators that can generate a specific language parser based on the language grammar definition. The parser generators like Generator Gardens (GPPG) [10], Point Parser GRAMMATICA - Parser Generator [11], ANTLR v3 [5] and Compiler Generator Coco/R [12] have been analyzed and the ANTLR v3 parser generator was chosen as the most suitable one for our purpose.

# B. Internal Representation of Structural Description

There are two basic approaches for internal data representation: an object-oriented approach and the XML based approach. An example of the *object-oriented structure representation* format is AIRE/CE (The Advanced Intermediate Representation with Extensibility/Common Environment) [13], a specification originally designed for the representation of VHDL description that can potentially be used for Verilog description as well.

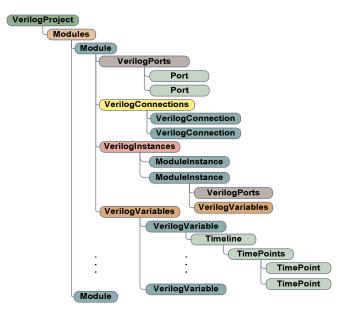

In general, the internal structure representation based on *XML* is more flexible than the object-oriented one. There are several specific XML schemes that could be used for our purpose including: HDML (Hardware Description Markup Language) [14] – an XML scheme created for hardware description, VXML [15] - the VHDL Markup Language scheme which is more suitable for VHDL description, MoML (Modeling Markup Language in XML) [16] - the XML scheme created for hardware design description like HDML. However, each of them would require some modifications to be tailored to Verilog language and our specific needs. Therefore we decided to design our own XML based representation. The reason was its higher flexibility and potential interoperability with third part XML editors. The resulting XML scheme is given in Fig. 3. The internal data representation will contain information about visualized structure as well as simulation results.

#### C. Graph Drawing Algorithms

Graph drawing, including optimization of modules and connections layout, is quite a complex problem. Several rules and algorithms are known for graph drawing and optimization that can be used for Verilog models visualization. The good graph look is very subjective issue, often it is just a matter of aesthetic taste, not the exact parameters. Therefore it is difficult to choose the best algorithm. In spite of this there are a few criteria for graph layout evaluation [17]:

*Minimize crossing:* keep the number of lines cross to a minimum.

*Minimize area:* keep the graph area to a minimum. *Minimize the sum of edge lengths.*

Fig. 3. The XML scheme of internal data representation

*Minimize the difference between edge lengths:* keep the edge lengths as same as possible.

Minimize bends: keep edge bends to a minimum.

## IV. VISUALISATION OF HDL SIMULATION

HDL model simulation is much more complicated than HDL model structure visualization. A testbench has to be developed to simulate the Verilog digital system model.

In the visualization process of Verilog model simulation a few basic steps can be identified. The first one is the Verilog code integrity and syntax checking. The second step is simulation itself and the third one is the transformation of simulation results into the internal representation and their visualization. There is also the possibility to visualize the simulation results from external VCD<sup>1</sup> (Value Change Dump) file. In this case the integrity of this file must be checked as well.

#### V. SYSTEM ARCHITECTURE

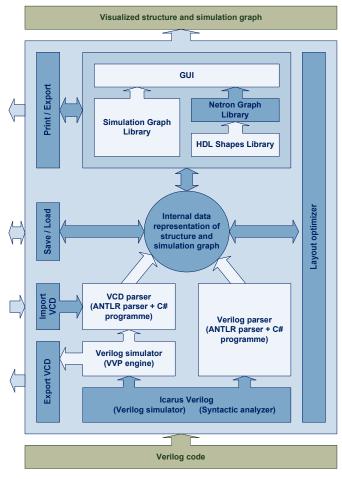

Based on the previous analysis the system architecture was designed that is illustrated in Fig. 4.

*The Icarus Verilog* was used to perform the syntactic analysis of Verilog model for its structure visualization as well as to simulate the model for simulation results visualization.

The syntactically correct Verilog model is passed to the *Verilog parser* that was implemented using the ANTLR v3 parser generator [5]. Only the Verilog language constructs relevant to structural description are parsed and transformed into the internal data representation: module definition, ports definitions, instantiations of modules and their mutual connections represented by "net" construct.

<sup>&</sup>lt;sup>1</sup> standardized format of simulation results

Fig. 4. The system architecture

Icarus Verilog simulator generates the simulation results in the form of VCD file – a textual description of variable values changes throughout the simulation time. A *VCD parser* is then used to perform the transformation of VCD data into the internal XML representation that was described in the previous section.

The *Layout optimizer* can be applied to the internal data to optimize the graphical layout of the visualized model. The goal of this optimization is symmetrical and well-arranged modules alignment and connections layout.

All the required application functionality is provided to the user by means of *Graphic User Interface* (GUI). To fulfill this task GUI cooperates with other components.

Simulation Graph Library component is used for drawing simulation results (Waveforms). It transforms the simulation results from internal XML form into an interactive simulation graph. The functions like zoom, time cursor, waves reordering and redrawing, image exporting or printing are supported by this library.

*Netron Graph Library* component is the core of the visualization. It carries our the actual drawing of modules, ports and interconnections and provides functions like objects moving, objects multi-selection, connections forming, graph printing and exporting, grid and snap to grid functions etc.

HDL Shapes Library component is an extension to Netron Graph Library. It defines the shapes of modules, connections, notes and pin labels. The basic classes for visualized objects: VerilogModule, VerilogPort and VerilogConnection are defined here. The objects of these classes represent the basic building elements of graph drawing. HDL Shapes Library is an interface between the Netron Graph Library and the internal XML representation. The classes for handling XML representation, modifying Verilog model visualization, and layout optimization are also defined here.

## VI. SYSTEM IMPLEMENTATION

The system was implemented in C# language under the .NET Framework 3.5 in Microsoft Visual Studio 2008 SP1 under the operating system Windows 7 Professional. The purpose of Verilog parser component is Verilog code parsing into the internal XML representation. It consists of three parts: VerilogLexer, VerilogParser, and VerilogToXML. The source codes of VerilogLexer and VerilogParser were generated by ANTLRv3 parser generator [5].

The VCD parser component is similar to the Verilog parser component. This component consists of three parts: VCDLexer, VCDParser, and VCDToXML. VCDLexer and VCDParser were also generated by ANTLRv3 parser generator.

HDL Shapes Library contains the definitions of classes like VerilogModule, VerilogPort and VerilogConnection that were derived from Netron Graph Library classes Shape and Connection. Other classes were implemented for handling XML representation, visualization and layout optimization.

The Simulation Graph Library provides an engine for creating interactive simulation graph (waveforms) user interface. This functionality is ensured by four main classes: Stamper, SimGraphControl, Wave and Header

## VII. RESULTS AND EXPERIENCE

All the implemented components have been tested during the implementation process and after that entire application was tested again. All found bugs have been fixed.

#### A. Illustrating Example

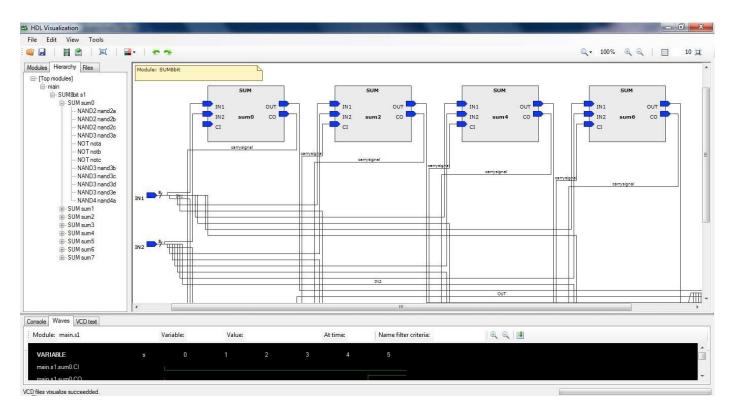

To illustrate the features of the implemented visualization tool a simple example will be presented here. In Fig. 5, there is a fragment of a simple Verilog model representing the structural description of 8-bit binary adder that was the input of the HDL Visualizator. The Verilog code is analyzed, simulated and transformed into an XML representation that is then visualized. The resulting visualization of Verilog structural description and its simulation illustrates the screenshot in Fig. 6.

## B. Restrictions

The application is able to recognize the following Verilog language constructions: module definition with module name and ports declaration, port type definitions, all types of net definitions (supply0, supply1, tri, triand, trior, tri0, tri1, wire, wand, wor), module instantiations, UDP (User Defined Primitive) definitions and UDP instantiations. Verilog parser can handle implicit port mapping or named port mapping in the module or UDP instantiation.

The vector type port can be assigned each vector element separately using curly brackets like in .portname ({sig1, sig2,

| <pre>module SUM8bit (IN1, IN2, OUT, CO);<br/>output [7:0] OUT;<br/>output [7:0] IN1;<br/>input [7:0] IN2;<br/>wire [6:0] carrysignal;<br/>SUM sum0(IN1[0],IN2[0], 0,OUT[0], carrysignal[0]);<br/>SUM sum2(IN1[2],IN2[1], carrysignal[1],OUT[2], carrysignal[1])<br/>SUM sum2(IN1[2],IN2[2], carrysignal[2],OUT[3], carrysignal[3])<br/>SUM sum3(IN1[3],IN2[3], carrysignal[3],OUT[4], carrysignal[3])<br/>SUM sum4(IN1[4],IN2[4], carrysignal[3],OUT[4], carrysignal[4])<br/>SUM sum5(IN1[5],IN2[5], carrysignal[3],OUT[6], carrysignal[6]).<br/>SUM sum6(IN1[6],IN2[6], carrysignal[6],OUT[6], carrysignal[6]).<br/>SUM sum7(IN1[7],IN2[7], carrysignal[6],OUT[7],CO);<br/>endmodule<br/>module main;<br/>reg [7:0] a,b;<br/>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •••         |                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------|

| <pre>output CO;<br/>input [7:0] IN1;<br/>input [7:0] IN2;<br/>wire [6:0] carrysignal;<br/>SUM sum0(IN1[0],IN2[0], 0,OUT[0], carrysignal[0]);<br/>SUM sum2(IN1[2],IN2[1], carrysignal[0],OUT[1], carrysignal[1])<br/>SUM sum2(IN1[2],IN2[2], carrysignal[2],OUT[3], carrysignal[3])<br/>SUM sum3(IN1[3],IN2[3], carrysignal[2],OUT[3], carrysignal[3])<br/>SUM sum4(IN1[4],IN2[4], carrysignal[3],OUT[4], carrysignal[4])<br/>SUM sum5(IN1[5],IN2[5], carrysignal[4],OUT[5], carrysignal[6]),<br/>SUM sum5(IN1[6],IN2[6], carrysignal[6],OUT[6], carrysignal[6]),<br/>SUM sum7(IN1[7],IN2[7], carrysignal[6],OUT[7],CO);<br/>endmodule<br/>module main;<br/>reg [7:0] a, b;<br/>wire [7:0] y,<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpvars(3, main );<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                                                   |

| <pre>input [7:0] IN1;<br/>input [7:0] IN2;<br/>wire [6:0] carrysignal;<br/>SUM sum0(IN1[0],IN2[0], 0,OUT[0],carrysignal[0]);<br/>SUM sum1(IN1[1],IN2[1],carrysignal[0],OUT[1],carrysignal[1]).<br/>SUM sum2(IN1[2],IN2[2],carrysignal[2],OUT[3],carrysignal[3])<br/>SUM sum3(IN1[3],IN2[3],carrysignal[3],OUT[4],carrysignal[4]).<br/>SUM sum6(IN1[6],IN2[6],carrysignal[3],OUT[6],carrysignal[4]).<br/>SUM sum6(IN1[6],IN2[6],carrysignal[5],OUT[6],carrysignal[6]).<br/>SUM sum6(IN1[6],IN2[6],carrysignal[6],OUT[6],carrysignal[6]).<br/>SUM sum7(IIN1[7],IN2[7],carrysignal[6],OUT[7],CO);<br/>endmodule<br/>module main;<br/>reg [7:0] a,b;<br/>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpfile( "SUM8bit.vcd" );<br/>\$dumpvars( 3, main );<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                                                   |

| <pre>input [7:0] IN2;<br/>wire [6:0] carrysignal;<br/>SUM sum0(IN1[0],IN2[0], 0,OUT[0],carrysignal[0]);<br/>SUM sum1(IN1[1],IN2[1],carrysignal[0],OUT[1],carrysignal[1]);<br/>SUM sum3(IN1[2],IN2[2],carrysignal[2],OUT[2],carrysignal[3]);<br/>SUM sum3(IN1[3],IN2[3],carrysignal[2],OUT[3],carrysignal[3]);<br/>SUM sum3(IN1[4],IN2[4],carrysignal[3],OUT[4],carrysignal[5]);<br/>SUM sum5(IN1[5],IN2[5],carrysignal[5],OUT[6],carrysignal[6]);<br/>SUM sum6(IN1[6],IN2[6],carrysignal[5],OUT[6],carrysignal[6]);<br/>SUM sum7(IN1[6],IN2[6],carrysignal[6],OUT[7],CO);<br/>endmodule<br/>module main;<br/>reg [7:0] a,b;<br/>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpfile( "SUM8bit.vcd" );<br/>\$dumpvars(3, main );<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                   |

| <pre>wire [6:0] carrysignal;<br/>SUM sum0(IN1[0],IN2[0], 0,OUT[0], carrysignal[0]);<br/>SUM sum2(IN1[0],IN2[1], carrysignal[0],OUT[1], carrysignal[1]);<br/>SUM sum2(IN1[2],IN2[2], carrysignal[2],OUT[3], carrysignal[3])<br/>SUM sum3(IN1[3],IN2[3], carrysignal[3],OUT[3], carrysignal[4]);<br/>SUM sum5(IN1[5],IN2[5], carrysignal[3],OUT[4], carrysignal[6]);<br/>SUM sum5(IN1[6],IN2[6], carrysignal[5],OUT[6], carrysignal[6]);<br/>SUM sum7(IN1[6],IN2[6], carrysignal[6],OUT[6], carrysignal[6]);<br/>SUM sum7(IN1[7],IN2[7], carrysignal[6],OUT[7],CO);<br/>endmodule<br/>module main;<br/>reg [7:0] a, b;<br/>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpAile( "SUM8bit.vcd" );<br/>\$dumpvars( 3, main );<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                                                   |

| $\begin{split} & \text{SUM sum0}( N1[0], N2[0], 0,OUT[0], carrysignal[0]); \\ & \text{SUM sum1}( N1[1], N2[1], carrysignal[0],OUT[1], carrysignal[1]), \\ & \text{SUM sum2}( N1[2], N2[2], carrysignal[2],OUT[3], carrysignal[3]), \\ & \text{SUM sum3}( N1[3], N2[3], carrysignal[3],OUT[3], carrysignal[3]), \\ & \text{SUM sum3}( N1[4], N2[4], carrysignal[3],OUT[3], carrysignal[4]), \\ & \text{SUM sum5}( N1[6], N2[5], carrysignal[3],OUT[6], carrysignal[4]), \\ & \text{SUM sum5}( N1[6], N2[6], carrysignal[3],OUT[6], carrysignal[4]), \\ & \text{SUM sum5}( N1[6], N2[6], carrysignal[5],OUT[6], carrysignal[6]), \\ & \text{SUM sum5}( N1[7], N2[7], carrysignal[6],OUT[7],CO); \\ & \text{endmodule} \\ & \text{module main;} \\ & \text{reg } [7:0] a, b; \\ & \text{wire } [7:0] a$ |             |                                                   |

| $ \begin{array}{l} {\displaystyle {\rm SUM  sum1(lN1[1],lN2[1],carrysignal[0],OUT[1],carrysignal[1])} \\ {\displaystyle {\rm SUM  sum2(lN1[2],lN2[2],carrysignal[2],OUT[2],carrysignal[2])} \\ {\displaystyle {\rm SUM  sum3(lN1[3],lN2[3],carrysignal[2],OUT[3],carrysignal[3])} \\ {\displaystyle {\rm SUM  sum3(lN1[4],lN2[4],carrysignal[3],OUT[4],carrysignal[4])} \\ {\displaystyle {\rm SUM  sum3(lN1[5],lN2[5],carrysignal[3],OUT[6],carrysignal[6])} \\ {\displaystyle {\rm SUM  sum5(lN1[5],lN2[6],carrysignal[6],OUT[6],carrysignal[6])} \\ {\displaystyle {\rm SUM  sum7(lN1[6],lN2[6],carrysignal[6],OUT[7],CO);} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                   |

| $\label{eq:starting} \begin{array}{l} SUM sum2(IN1[2],IN2[2],carrysignal[1],OUT[2],carrysignal[2]),\\ SUM sum3(IN1[3],IN2[3],carrysignal[3],OUT[4],carrysignal[3]),\\ SUM sum3(IN1[4],IN2[4],carrysignal[3],OUT[4],carrysignal[5]),\\ SUM sum5(IN1[5],IN2[5],carrysignal[5],OUT[6],carrysignal[6]),\\ SUM sum6(IN1[6],IN2[6],carrysignal[5],OUT[6],carrysignal[6]),\\ SUM sum7(IN1[7],IN2[7],carrysignal[6],OUT[7],CO);\\ endmodule main; \\ reg [7:0] a,b; \\ wire [7:0] y; \\ wire co; \\ time tim; \\ SUM8bit s1(a,b,y,co); \\ initial begin \\ \\ \begin{array}{l} SUM sum5(IN1[6],SUM8bit.vcd"); \\ $dumpvars(3, main); \\ a = 0; \\ b = 0; \\ \#1 a = 2; \\ \#1 b = 15; \end{array} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SUM sum     | U(IN1[U],IN2[U], U,UUI[U],Carrysignal[U]);        |

| $ \begin{array}{l} {\rm SUM \ sum3(IN1[3],IN2[3],carrysignal[2],OUT[3],carrysignal[3])} \\ {\rm SUM \ sum4(IN1[4],IN2[4],carrysignal[3],OUT[4],carrysignal[4])} \\ {\rm SUM \ sum5(IN1[5],IN2[5],carrysignal[3],OUT[6],carrysignal[6])} \\ {\rm SUM \ sum6(IN1[6],IN2[6],carrysignal[6],OUT[7],CO);} \\ {\rm endmodule} \\ {\rm module \ main;} \\ {\rm reg \ [7:0] \ a,b;} \\ {\rm wire \ [7:0] \ a,b;} \\ {\rm wire \ [7:0] \ y;} \\ {\rm wire \ co;} \\ {\rm time \ tim;} \\ {\rm SUM \ sum7(IN1[7],IN2[7],carrysignal[6],OUT[7],CO);} \\ {\rm initial \ begin} \\ {\rm \ SUM \ sum7(IN1[7],IN2[7],carrysignal[6],OUT[7],CO);} \\ {\rm \ initial \ begin} \\ {\rm \ SUM \ sum7(IN1[7],IN2[7],CO);} \\ {\rm \ initial \ begin} \\ {\rm \ Sum8bit \ s1(a,b,y,co);} \\ {\rm \ initial \ begin} \\ {\rm \ Sum8bit \ s1(a,b,y,co);} \\ {\rm \ a \ = \ 0;} \\ {\rm \ b \ = \ 0;} \\ {\rm \ #1 \ a \ = \ 2;} \\ {\rm \ #1 \ b \ = \ 15;} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                                                   |

| SUM sum4(IN1[4],IN2[4],carrysignal[3],OUT[4],carrysignal[4])<br>SUM sum5(IN1[5],IN2[5],carrysignal[4],OUT[5],carrysignal[5])<br>SUM sum7(IN1[6],IN2[6],carrysignal[6],OUT[6],carrysignal[6])<br>SUM sum7(IN1[7],IN2[7],carrysignal[6],OUT[7],CO);<br>endmodule<br>module main;<br>reg [7:0] a,b;<br>wire [7:0] y;<br>wire co;<br>time tim;<br>SUM8bit s1(a,b,y,co);<br>initial begin<br>Sdumpfile( "SUM8bit.vcd" );<br>Sdumpvars( 3, main );<br>a = 0;<br>b = 0;<br>#1 a = 2;<br>#1 b = 15;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                                                   |

| <pre>SUM sum5(IN1[5],IN2[5],carrysignal[4],OUT[5],carrysignal[5]),<br/>SUM sum6(IN1[6],IN2[6],carrysignal[5],OUT[6],carrysignal[6]),<br/>SUM sum7(IN1[7],IN2[7],carrysignal[6],OUT[7],CO);<br/>endmodule<br/>module main;<br/>reg [7:0] a,b;<br/>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpfile( "SUM8bit.vcd" );<br/>\$dumpvars( 3, main );<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                                   |

| <pre>SUM sum6[IN1[6],IN2[6],carrysignal[5],OUT[6],carrysignal[6]),<br/>SUM sum7(IN1[7],IN2[7],carrysignal[6],OUT[7],CO);<br/>endmodule<br/>module main;<br/>reg [7:0] a,b;<br/>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpVarl(1",SUM8bit.vcd");<br/>\$dumpvars(3, main);<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                                                   |

| SUM sum7(IN1[7],IN2[7],carrysignal[6],OUT[7],CO);<br>endmodule<br>module main;<br>reg [7:0] a,b;<br>wire [7:0] y;<br>wire co;<br>time tim;<br>SUM8bit s1(a,b,y,co);<br>initial begin<br>\$dumpfile( "SUM8bit.vcd" );<br>\$dumpars( 3, main );<br>a = 0;<br>b = 0;<br>d = 2;<br>#1 a = 2;<br>#1 b = 15;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                                                   |

| endmodule<br>module main;<br>reg [7:0] a,b;<br>wire [7:0] y;<br>wire co;<br>time tim;<br>SUM8bit s1(a,b,y,co);<br>initial begin<br>\$dumpfile( "SUM8bit.vcd" );<br>\$dumpvars( 3, main );<br>a = 0;<br>b = 0;<br>#1 a = 2;<br>#1 b = 15;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                   |

| <pre>module main;<br/>reg [7:0] a,b;<br/>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpvars( 3, main );<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | /(iiiii/),iiii//,iiii/oib/iii/oib/ii///////////// |

| reg [7:0] a,b;<br>wire [7:0] y;<br>wire co;<br>time tim;<br>SUM8bit s1(a,b,y,co);<br>initial begin<br>\$dumpfile( "SUM8bit.vcd" );<br>\$dumpvars( 3, main );<br>a = 0;<br>b = 0;<br>#1 a = 2;<br>#1 b = 15;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | n.                                                |

| <pre>wire [7:0] y;<br/>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpfile( "SUM8bit.vcd" );<br/>\$dumpvars( 3, main );<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                                                   |

| <pre>wire co;<br/>time tim;<br/>SUM8bit s1(a,b,y,co);<br/>initial begin<br/>\$dumpvars(3, main);<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                                   |

| SUM8bit s1(a,b,y,co);<br>initial begin<br>\$dumpfile( "SUM8bit.vcd" );<br>\$dumpvars( 3, main );<br>a = 0;<br>b = 0;<br>#1 a = 2;<br>#1 b = 15;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                                                   |

| initial begin ''''''''''''''''''''''''''''''''''''                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | time tim;   |                                                   |

| <pre>\$dumpfile("SUM8bit.vcd");<br/>\$dumpvars(3, main);<br/>a = 0;<br/>b = 0;<br/>#1 a = 2;<br/>#1 b = 15;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SUM8bit     | s1(a,b,y,co);                                     |

| \$dumpvars( 3, main );<br>a = 0;<br>b = 0;<br>#1 a = 2;<br>#1 b = 15;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | initial beg | in                                                |

| a = 0;<br>b = 0;<br>#1 a = 2;<br>#1 b = 15;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -           | \$dumpfile( "SUM8bit.vcd" );                      |